在如今的电路设计之中,无论是DC-DC开关电源还是LDO都有完善的反馈特性能够完成很好的压控设计目标,在一些场景之中为了防止反接常常使用一些物理防呆接口——但是俗话说的好:防呆不防傻,大力出奇迹。所以对于过高的电压、反接电源烧毁电路还是需要注意,这时候我们可以使用P沟道MOSFET非常轻松的完成这些电路,实现很好的效果。

1. 整体原理图分析

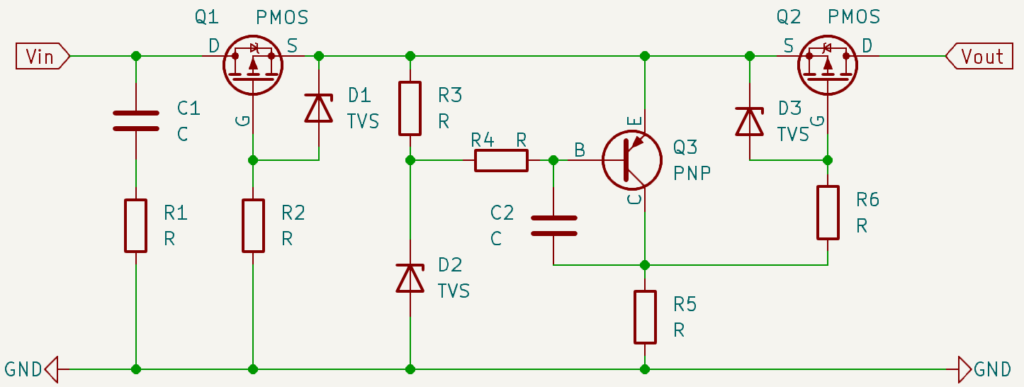

上图之中大致可以分成两部分,在R3-D2左侧的是防反接电路,右侧的是过压保护和缓启动电路。我们首先来分析PMOS防反接电路:可以发现P沟道MOSFET的Q1处于反向驱动状态,我们期望的电流方向是从D到S流动,使用体二极管做前置,让我们首先不考虑C1,R1,R2,D1,认为Q1的栅极(G)直接接入GND:

- 如果\(V_{in}>0\)并且后级电路没有上电,那么体二极管正向偏置导通,将Q1-S处电压拉高,这时候对于Q1而言\(V_{gs}=V_g-V_s=-V_s=V_{in}-V_{Q1,Diode}\)只要这个电压值大于开通阈值电压\(V_{Q1,threshold}\)那么Q1开通,电路正常工作。

- 如果\(V_{in}<0\)也就是出现了电源反接的状况,只要\(V_{in}\)不超过Q1的提二极管的击穿电压,那么即使体二极管反向偏置也不会击穿,这时候G和S都相当于接地,压差不超过开通阈值电压,整个P-MOS处于关断状态,电路不开放电流通道,完成了防反接。

电路之中的R1和C1事实上是构成了一个简易的RC滤波器,这两个器件应当选择较小的容值和阻值,这样就能够滤除电源输入中的高频小幅值噪声。R2和D1的作用是保护MOS管栅极,R2用于限流并且 提供在D1反向击穿时的电流通路;D1是一个齐纳二极管,它工作在反向状态,这个管子的反向击穿电压应当小于Q1的最大G-S电压,这样一来假设\(V_{in}\)过大它就会将G-S之间的电压钳位到它本身的击穿电压,从而保护了PMOS不被从栅极击穿。

在右侧的电路之中我们可以发现Q2也有R6,D3作为这样的栅极保护电路。事实上这部分电路主要完成两个任务:缓启动和过压保护。Q3的PNP三极管用于控制Q2的通断,而完成过压保护的核心就是R3-D2构成的钳位电路,让我们分析一下:

- 假设经过了防反接电路的直流母线电压是\(V_{DC}\),那么在选取器件时假设这个电压可能超过我们希望的最大电压,我们就要将D2的反向击穿电压选择为我们希望的\(V_{max}\)。

- 如果\(V_{DC}\le V_{max}\)那么虽然D2反向偏置但是不足以击穿,此时可以认为这个二极管不存在,\(V_{Q3,B}\)相当于被上拉到\(V_{DC}\)——E-B结没有足够的正向偏置电压,三极管不导通,相当于断路。那么栅极相当于被R5,R6下拉接地,Q2因为G-S电压超过开通阈值而导通,后级电路就可以得到正常供电。

- 如果\(V_{DC}> V_{max}\)那么D2反向偏置并且击穿,将R3与它之间结点的电压钳位到\(V_{max}\),此时R3承受的电压就是\(V_{DC}-V_{max}\),故而R3应当选择一个较大的阻值以减小流过的电流从而降低热功。只要\(V_{DC}-V_{max}\ge -V_{Q3,BE}\)那么三极管就将开通,并且因为此时E-B结正向偏置开通,故而B处的电压会被钳位到\(V_{DC}-(-V_{Q3,BE})\),这就是R4存在的必要性,因为B处的电压经过钳位后不会完全等于R3低压侧的电压。由于三极管开通,所以栅极相当于通过三极管上拉到\(V_{DC}-V_{Q3,saturation}\),因此只要PNP三极管的饱和导通压降低于开通阈值就会使MOS管保持关断,后级电路不会供电。

- C2起到缓启动的作用,由于电容两端的电压不能突变,因而在上电时的一瞬间,C2会强制令集电极上的电压保持与基极相同,随后通过电阻慢慢放电降低集电极上的电压,给栅极通入电流开通MOS管,而放电的时间就是所谓的缓启动时间,在这个过程之中网络输出侧的电压和电流都会缓慢攀升。

这里补充两点:在防反接电路的构建方法之中,也可以在电源的回流路线,也就是上图之中的GND上增加一个N-MOS管组建和本方案相似的电路,只不过这样会使得电源地并不等于后级电路地平面的电压,笔者不喜欢这种方式因而不采用这种方案,但这并不意味着这种方案不可用。第二就是C2也可以直接接在Q2的栅极和源极之间,增加MOS管导通过程之中的米勒时间,两种方案大同小异。

2. LT-Spice仿真验证

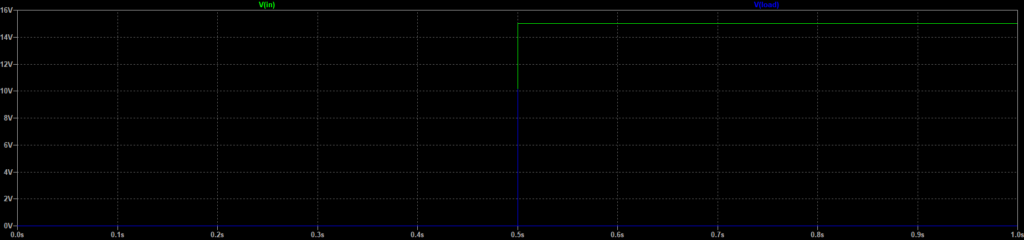

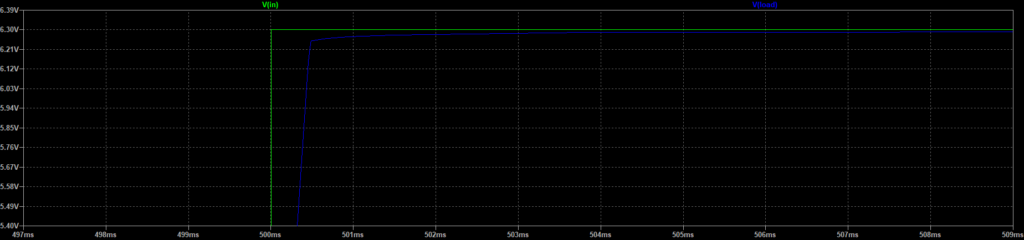

以上是笔者在LT-Spice之中简单搭建的仿真电路,设定的过压保护值为9.1V,使用一个\(100\Omega\)的电阻作为,模拟负载。P-MOS和PNP实际上是随便选的,除非做实际电路的时候完全不关心选型或者应用条件非常恶劣,这个电路实际上不是很挑参数,以下是反接、过压、正常接入电源时的波形:

上述三个模拟的电源都在0.5s时产生开关动作,分别是-10V(反接情况)、+10V(过压情况)、+6.3V(正常缓启动状况)三种,可以发现在反接和过压切换瞬间出现了一个尖峰(这种状况有仿真不完全贴合实际的一面也有参数选择的小问题)之外符合预期,感兴趣者可以下载仿真文件。

多次插拔时,c2 电容需要放电回路吗?

在这种电路设计之中C2的作用是利用电容两端电压不突变的特性使Gate上的电压以指数衰减的形式开通MOSFET,C2的大小决定了这个时间的长短——通常来说不会比人操作接插件时手抖的时间长。当断电时其中存储的电荷会通过电阻耗散所以我认为不必加入放电回路——因为C2也就1-10uF。如果您想要更长的母线压升时间,您可以考虑在母线上面并联一个巨大的电容,并且单独对那个大电容进行充放电管理。这个电路之中的缓启动通常是考虑到很多器件,例如钽电容无法承受过高的dv/dt而存在的,其目的并不是为了获得一个人类操作速度(秒)级别的延迟。